Разобравшись с устройством программы можно попробовать написать что нибудь простенькое вроде мигания диодом. Но для начала я предлагаю разобраться с тем что можно добавлять в проект (после нажатия Ctrl+n ).

1) Block Diagram/ Schematics File - Это лист с Принципиальной схемой. Логичнее всего поставить в самый верх иерархии, для наглядного соединения разработанных модулей на hdl с портами ПЛИС.

2) AHDL (Altera HDL) - Язык описывающий то как должны быть устроены схемы. Хорошее описание можно найти в этой статье и этой презентации, а так же я возможно сделаю статью конспект. Это язык компании Altera, поэтому в нем есть конструкции описывающие элементы ПЛИС именно этой фирмы, например D-триггер. Главное, что знак = значит не равенство или присвоение, а физическое соединение выводов.

3) Verilog HDL file - Язык описывающий то что должна делать аппаратура. Более высокоуровневый по сравнению с AHDL. Про него можно узнать в книге "Цифровая схемотехника и архитектура компьютера" ее электронная версия бесплатна.

4) System Verilog HDL file - Язык описывающий то что должна делать аппаратура. Развитие языка Verilog. В 2009 был объединен со стандартом языка Verilog. Это будет основным языком разработки.

5) VHDL file - Почти то же самое что и System Verilog, но более многословный и не похож на С. Так что его обойдём стороной.

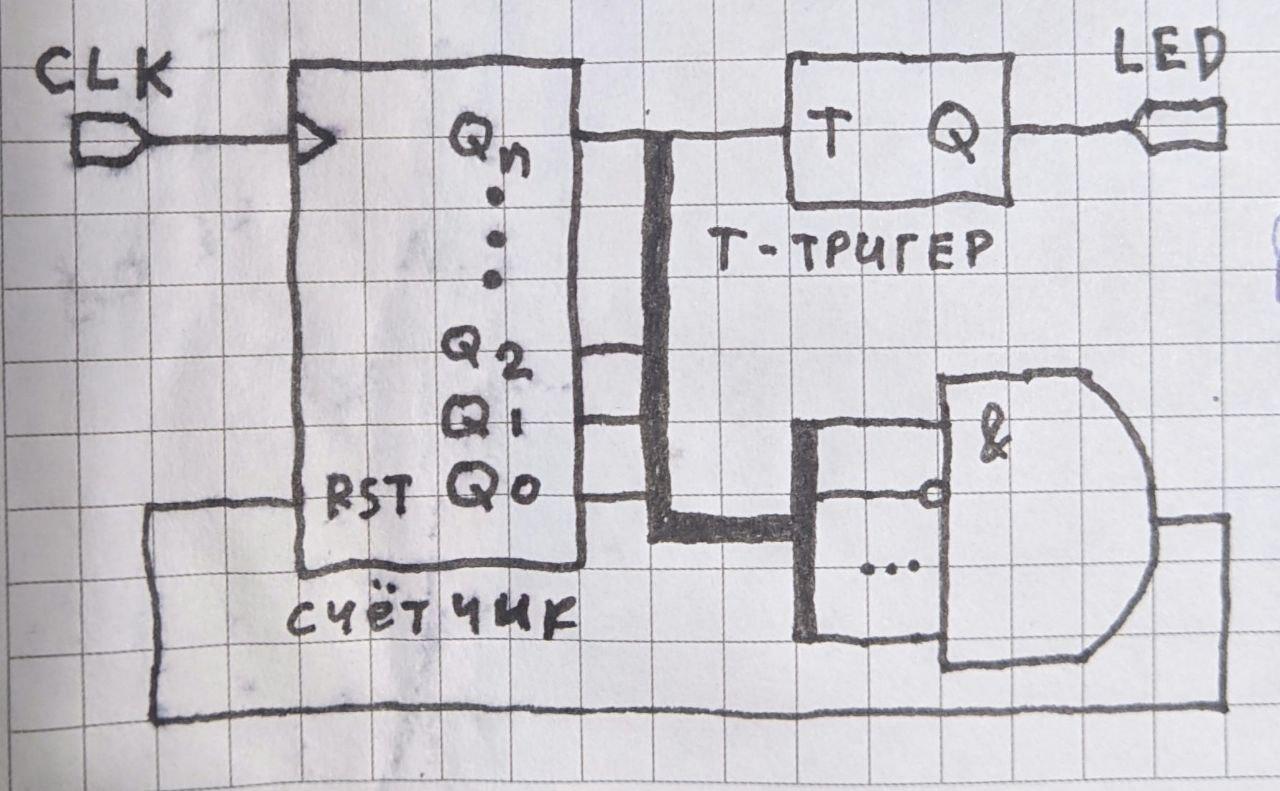

Для начала предлагаю в общем виде представить из чего может состоять схема мигания диодом, на ум приходит что-то вроде такого:

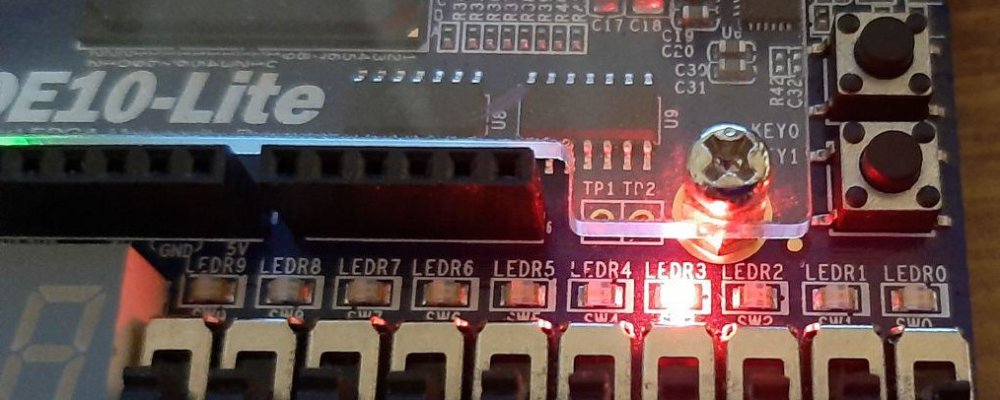

Далее необходимо посмотреть какие периферийные блоки на отладочной плате помогут нам это реализовать. Это тактовый генератор и диод.

Генератор 50MHz - Это значит, что для мигания с частотой 1 Hz счетчик должен досчитывать до 50000000, а потом сбрасываться. 50 миллионов это 2 FA F0 80 в HEX, а значит нужен 26-битный счетчик.

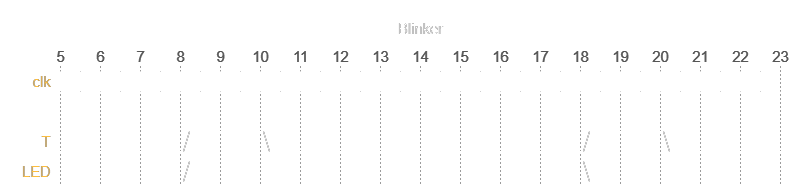

В предложенной схеме мы подключаем сигнал тактового генератора к счетчику, а его старший разряд к Т-триггеру. Это позволит менять состояние триггера, каждый раз когда старший разряд счетчика переходит в единицу. Временная диаграмма бля него будет выглядеть так. Она, кстати, сделана с помощью этого сервиса:

Для того чтобы у нас была возможность сбросить счетчик по любому значению необходимо все выходы со счетчика соединить элементом И или ИЛИ, выход которого отправить на сброс счетчика. Таким образом добавляя элемент НЕ на входы И или ИЛИ можно выставить любое число для сброса, главное чтобы оно было не меньше чем разрядность счетчика, т.к. в этом случае старший бит никогда не станет единицей.

Быстрее всего данный модуль будет реализовать с помощью ahdl, а соединить модуль с физическими выводами можно уже на схеме. Возьмем проект из прошлой статьи там как там уже создан Schematics файл. Открыв проект создадим лист ahdl (комбинация ctrl+n).

Далее предлагаю минимально ознакомится с AHDL. Модуль AHDL состоит из следующих блоков:

- Блок объявления входов/выходов

- Блок объявления внутренних элементов схемы

- Блок логического описания

Как можно догадаться в первой секции нужно прописать пины (CLK - тактирующий вход и Q - выход для диода) и название модуля (Count):

subdesign Count (

CLK:input;

Q:output;

)Во втором блоке нужно объявить элементы входящие в схему, у нас это 2 буфера: cnt[25..00] - массив из 25 D-триггеров (DFF) для реализации 26-битного счетчика и один T-триггер (TFF) buf.

variable

cnt[25..0] : DFF;

buf : TFF;В третьем блоге описываются взаимосвязи между компонентами. Главное помнить что знак = это не знак равенства, а физическое соединение проводников и все выражения с этим знаком будут исполняться параллельно.

begin

cnt[].clk = CLK; --тактирование массива триггеров от генератора

Q = buf.q; --Выход схемы - выход Т-триггера

buf.clk = cnt[25]; --Т-триггер выставляется старшим битом массива

buf = vcc; --Так надо, из-за особенности реализации Т-триггера

if cnt[] == 50000000 then --считаем до 5 млн

cnt[] = 0;

else

cnt[] = cnt[] + 1;

end if;

end;Эта статья не ставит целью объяснить работу с AHDL, а лишь показывает процесс работы со средой Quartus, поэтому приведён срезу готовый код с комментариями.

Далее из полученного кода необходимо создать символ для схемы.

Далее вернемся к схеме полученной в прошлой статье, удалим соединение и поставим созданный нами блок между компонентами. Для Этого на схеме нужно выбрать insert -> Symbol..., а далее выбрать его.

Потом удаляем вход с кнопки и ставим вместо него вход с тактового генератора, чтобы получилось следующее:

Теперь можно компилировать и запускать на fpga, диод должен начать мигать.

Далее если выбрать Tools->Netlist Viewers->RTL Viewer то можно увидеть то что сгенерила программа.

Это очень похоже на нашу начальную схему.

Замечания

Чтобы подключить ModelSim-Altera нужно в

Tools->Options... -> General -> EDA Tool Option -> ModelSimдобавить

/intelFPGA_lite/<version>/modelsim_ase/win32aloem (Lite)