В разработке под fpga есть одна проблема которая меня всегда очень раздражала, это необходимость использования огромных и тормозных IDE. Поэтому сегодня разберемся с открытым стеком технологий для разработки под FPGA.

Работать будем с icestorm — это проект с открытым исходным кодом, инициированный Клиффордом Вольфом в 2015 году. Это набор инструментов для временного анализа, упаковщика и прошивальщика (только через FT2232HL). Если к этому добавить программу для синтеза (yosys) и трассировки (nextpnr), то можно реализовать полный цикл разработки. Это значит что мы можем просто установить несколько легковесных программ из apt и сразу начать работать.

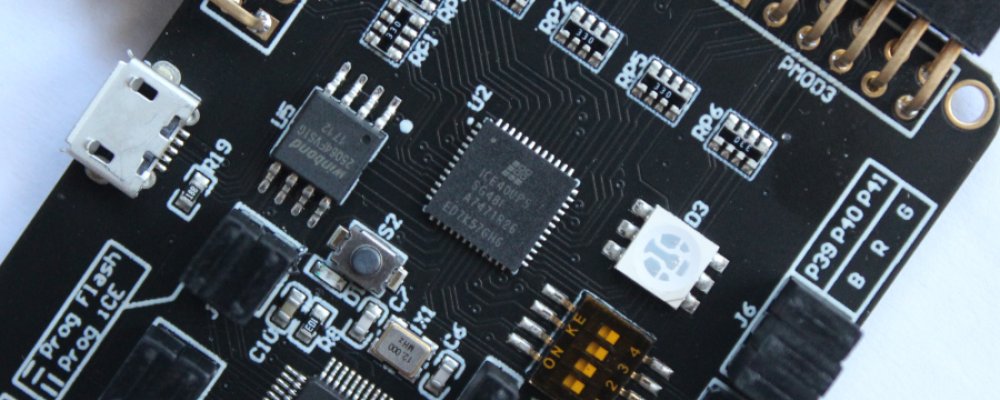

Для работы мы будем использовать плату iCESugar, купленной мной здесь (однако на момент написания данной статьи в начале ее в наличии не было), сразу в наборе с кучей различных модулей Pmod. Подробнее про нее можно прочитать в блоге автора, надеюсь вас не остановит то что он на китайском. Здесь же, я отражу основные интересные моменты.

В данной плате как программатор используется iCELink, что по своей сути является измененным DAPLink. Из-за этого мы не можем прошить fpga используя iceprog, возможно только закинуть собранный бинарь в программатор (он создает блочное устройство при подключении к компьютеру) что приведет к записи его на микросхему флеш памяти, с которой грузится конфигурация fpga при старте. Загрузить бинарь сразу в fpga минуя запись во flash мы не можем, зато данный программатор имеет ряд других интересных фитч. В случае если мы зашьем в FPGA софт процессор с поддержкой jtag можно будет использовать дынный программатор как jpag отладчик для soft процессора. Также он создает виртуальный COM порт, и тактирует fpga 12Mhz. Схему данной платы можно посмотреть тут.

Установка среды.

Для начала необходимо установить необходимые пакеты:

sudo apt install yosys nextpnr-ice40 iverilog gtkwave fpga-icestormГде:

- yosys - фреймворк для синтеза verilog RTL.

- nextpnr-ice40 - трассировщик для ice40 fpga.

- iverilog - открытый verilog симулятор.

- gtkwave - программа для отрисовки временных диаграмм из iverilog.

- fpga-icestorm - набор по для работы непосредственно с ice40 fpga.

Собственно этого уже достаточно для работы.

Минимальный пример

Для того чтобы убедится в работоспособности платы запустим код мигания диодом. Для этого нам потребуется 3 файла:

- Сама программа на языке verilog

top.v. - Файл с описанием физических портов

io.pcf. - Скрипт для сборки

Makefile.

С кодом на verilog все просто, делаем счетчик по фронту тракторующего сигнала, и подключаем RGB светодиод к 3-м последним разрядам:

module top(input clk, output LED_R, output LED_G, output LED_B);

reg [25:0] counter = 0;

assign LED_B = ~counter[25];

assign LED_R = ~counter[24];

assign LED_G = ~counter[23];

always @(posedge clk)

begin

counter <= counter + 1;

end

endmodule //topС описанием портов тоже нет особых проблем, просто перечисляем используемые пины и присваиваем им имена (сразу вместе со всей остальной периферией на плате):

# For the iCESugar Board (iCE40UP5K-QFN48)

set_io LED_G 41

set_io LED_R 40

set_io LED_B 39

# 12Mhz for iCELink

set_io clk 35

set_io RX 4

set_io TX 6

set_io USB_DP 10

set_io USB_DN 9

set_io USB_PULLUP 11

#spi

set_io SPI_SS 16

set_io SPI_SCK 15

set_io SPI_MOSI 17

set_io SPI_MISO 14Последнее что нужно это скрипт - Makefile:

# Set your parametrs

PROGECT_NAME = template

PCF_FILE = io.pcf

TOP_MODELE = top

# Write your verilog file.

VERILOG_FILES = \

$(TOP_MODELE).v

ICELINK_DEV = /dev/$(shell lsblk -f | grep iCELink | cut -d ' ' -f 1)

ICELINK_DIR = /tmp/iCELink

build:

yosys -p "synth_ice40 -top $(TOP_MODELE) -json $(PROGECT_NAME).json" $(VERILOG_FILES)

nextpnr-ice40 \

--up5k \

--package sg48 \

--json $(PROGECT_NAME).json \

--pcf $(PCF_FILE) \

--asc $(PROGECT_NAME).asc

icepack $(PROGECT_NAME).asc $(PROGECT_NAME).bin

flash:

mkdir -p $(ICELINK_DIR)

mount $(ICELINK_DEV) $(ICELINK_DIR)

cp $(PROGECT_NAME).bin $(ICELINK_DIR)

sync

umount $(ICELINK_DIR)

clean:

rm $(PROGECT_NAME).*Данный скрипт ожидает что ваш top модуль будет находится в файле с названием как и у верхнего модуля, также его название необходимо вписать в TOP_MODELE. Так-же при желании можно прописать название проекта.

На этом нюансы не заканчиваются. Т.к. в роле программатора на плате используется iCELink то прошить fpga нельзя. Прошить fpga можно только при помощи перетаскивания файла прошивки внутрь программатора. Поэтому в makefile сначала создается папка для монтирования программатора (в /tmp/) как блочного устройства. После чего ищем адрес программатора в /dev/ через lsblk, поле чего монтируем его в /tmp/iCELink. Так сделано специально, чтобы следов данной папки не оставалось после перезагрузки системы.

Если в вашей системе настроено автоматическое монтирование наситилей (например если вы используете ubuntu) то данный makefile работать не будет. Это связанно с тем что команда mount завершится ошибкой, выдав ошибку о том, что том уже смонтирован. Версию Mekefile для автоматически смонтированного устройства можно посмотреть тут.

Для того чтобы собрать и загрузить код необходимо выполнить следующие команды:

make

sudo make flashДалее я предлагаю рассмотреть чуть подробнее ПО которое используется нами для работы.

Yosys

Yosys написана на С++ позволяет преобразовать Verilog файлы в BLIF (Berkeley Logic Interchange Format) / EDIF (Electronic Design Interchange Format) и другие форматы. По сути синтезирует связи для FPGA. Данный пакет позволяет работать с FPGA Xilinx 7-Series и Lattice iCE40.

В makefile использовалась команда, эквивалентная этой:

yosys -p "synth_ice40 -top top -json led.json" led.vПо сути тут 2 параметра - это название verilog файла который читаем для анализа и скрипт который мы передаем в двойных кавычках после ключа -p. В данном скрипте мы запускаем макрос synth_ice40 необходимый для синтеза под ice40. Другие макросы для других fpga можно глянуть тут. Данному макросу необходимо передать параметры - название верхнего модуля -top top, и имя json файла куда записать результат синтеза -json led.json.

Есть альтернативный способ использование данного ПО - вручную, а не через makefile.

yosysДалее перед нами появится консоль, работа с программой состоит из поочередного вызова команд разных этапов работы с verilog файлом. Основные команды:

- read_verilog - читает verilog файла;

- hierarchy - составляет иерархию verilog файла или проекта;

- proc - обрабатывает always блоки;

- opt - проводит оптимизацию, если возможна;

- techmap - позволяет выполнить отображение каждого элемента схемы;

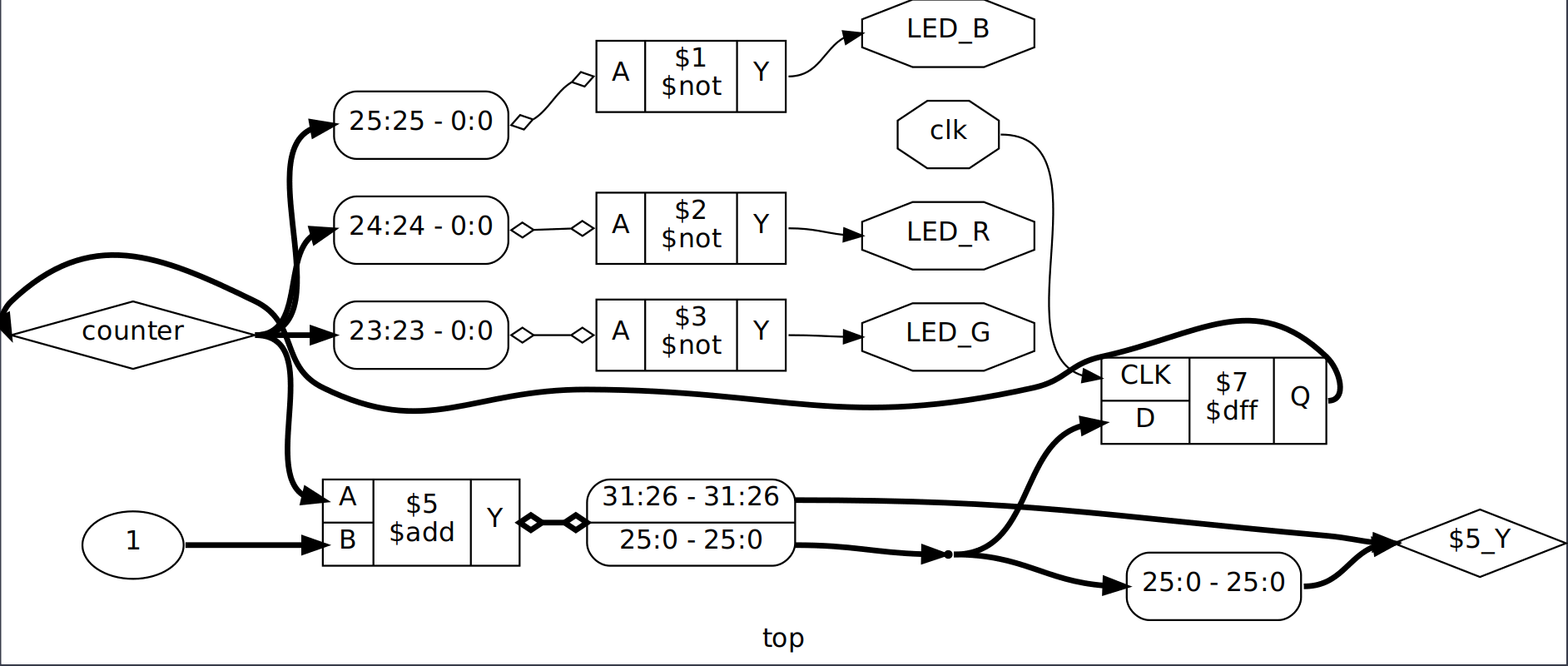

- show - отобразить схему устройства в графическом виде. Создается dot файл и отображается с помощью Graphviz.

yosys> read_verilog led.v

yosys> hierarchy

yosys> proc

yosys> opt

yosys> show

yosys> techmap

yosys> showПервый show выдаст схему уровня RTL, второй покажет связи на уровне lut. Схемы не очень читабельны, возможно это можно как-то поправить, но я не разбирался с этим.

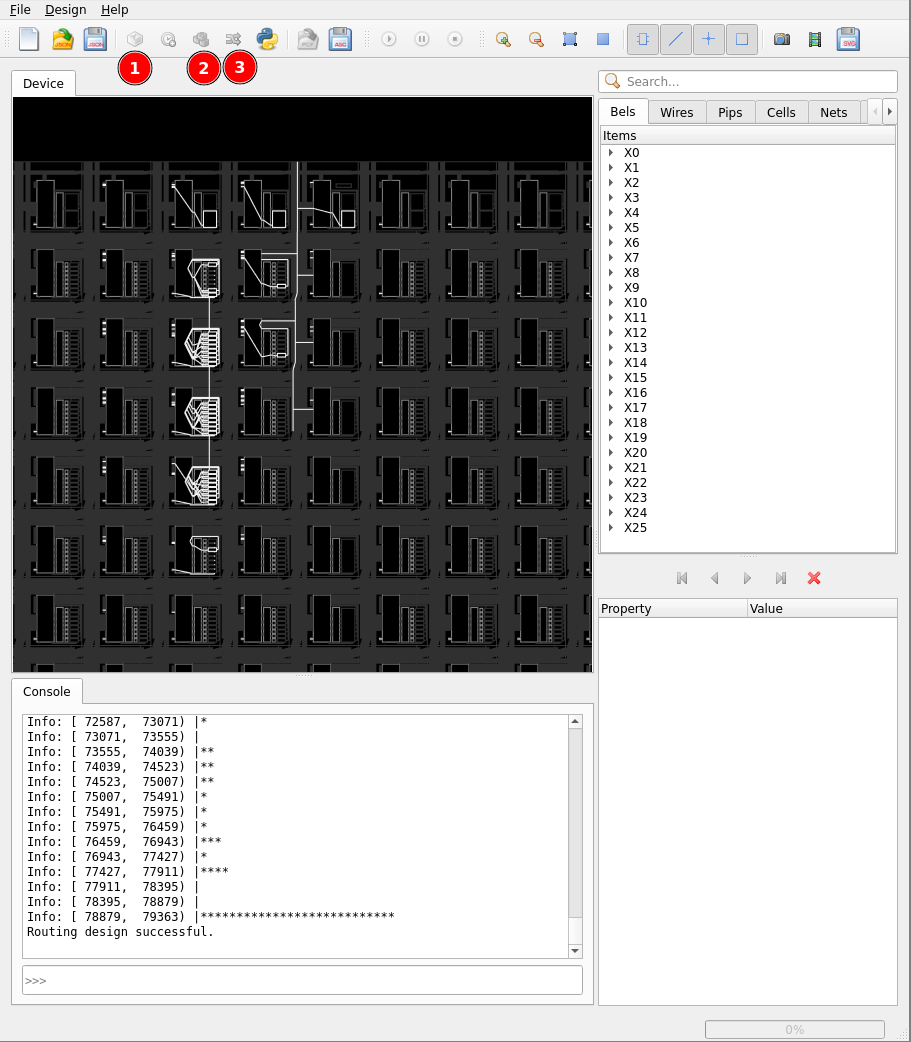

nextpnr-ice40

Для ручного запуска данного программного пакета нужно выполнить следующую команду:

nextpnr-ice40 --up5k --package sg48 --json led.json --pcf io.pcf --asc led.ascТакже данную программу можно запустить в графическом режиме, однако для этого нужно до установить через apt следующий пакет: nextpnr-ice40-qt.

nextpnr-ice40 --up5k --package sg48 --json led.json --pcf io.pcf --asc led.asc --guiДля отображения связей необходимо проделать цепочку команд: Pack->Place->Route.

Icestorm

icestorm содержит в себе следующие пакеты:

- IcePack/IceUnpack - программа запаковщик/распаковщик прошивки в бинарный файл, все icestorm утилиты используют ASCII формат.

- Icetime - программа для простого временного анализа, или собрания файлов для внешних программ временного анализа.

- IceProg - Программа для прошивки чипов через FTDI программаторы.

- IceMulti - Запаковщик нескольких бинарных файлов в один образ.

- IcePLL - программа для расчета параметров конфигурации iCE40 PLL.

- IceBRAM - программа для подкачки содержимого BRAM FPGA в ASCII файл.

Нам же из этого всего нужна только одна программа - icepack:

icepack led.asc led.binт.к. для прошивки используется просто перетаскивание файла в папку программатора.

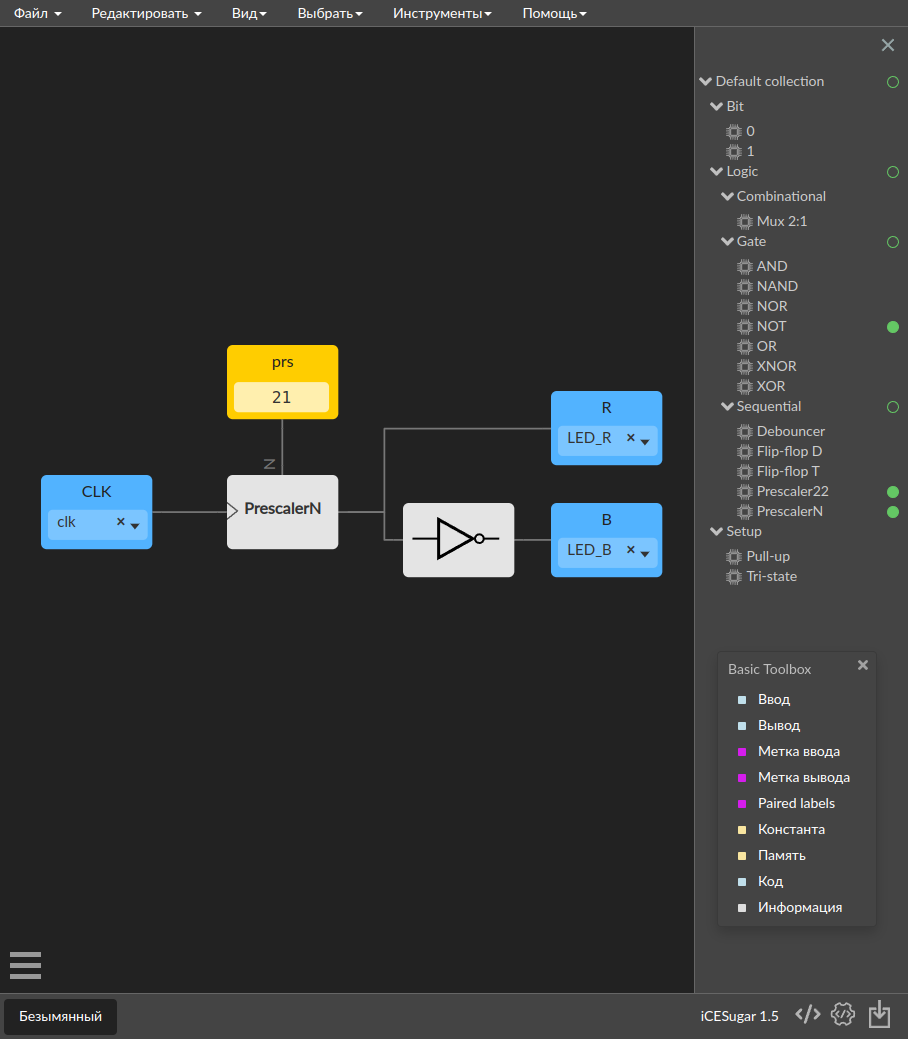

Icestudio

Также мной была найдена крайне занятная IDE для графического программирования fpga - Icestudio, в которой есть поддержка рассматриваемой платы. Данная программка написана поверх хрома (electron), и работает на питоне, создавая виртуальную среду исполнения в папке ~!/.icestudio, и после работы данная папка весит около гигабайта. Как серьезное средство разработки, я бы не стал рассматривать данную программу, но пособирать немного схемки в графическом режиме вполне можно.

Для установки необходимо доставить следующие зависимости:

sudo apt install python3 python3-pip python3-venv xclipПосле чего скачиваем архив с appimage отсюда, распаковываем, даем права на запуск и запускаем:

chmod +x icestudio-0.9.1w202204070704-linux64.AppImage

./icestudio-0.9.1w202204070704-linux64.AppImageДалее необходимо установить необходимые наборы инструментов, это будет предложено сделать в gui, максимально подробно это описано тут. После чего предложат установить драйвера, тоже соглашаемся. Все можно тыкать.

Из не очевидных моментов - это то что для открытия Basic Toolbox необходимо нажать Ctrl + T или Редактировать->Toolbox. Это меню необходимо для выбора входов и выходов в плате. Базовые компоненты находятся в Default collection справа. Если их недостаточно, то можно до установить другие коллекции.

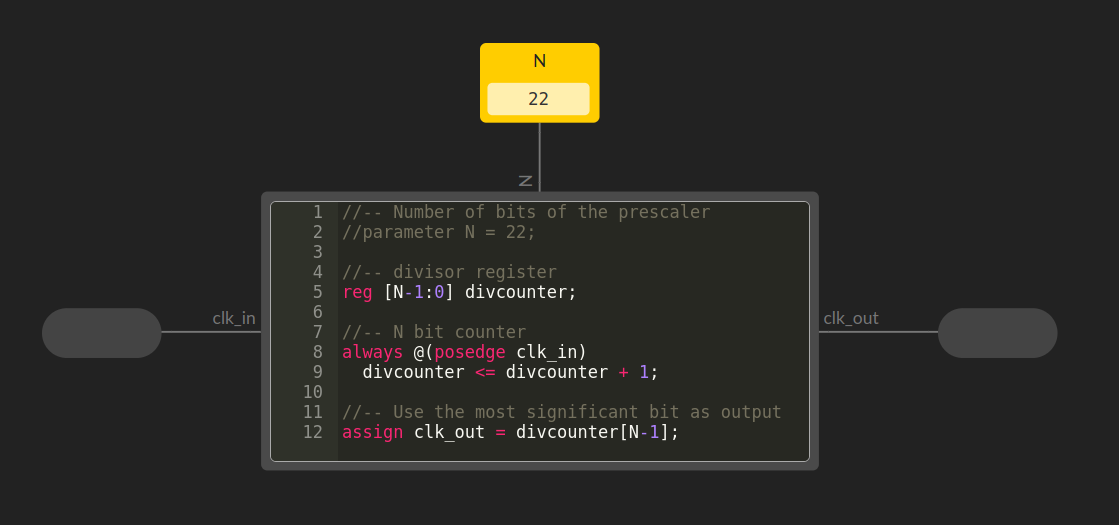

По своей сути каждый блок это просто кусок кода написанного на verilog, например блок делителя частоты:

Есть возможность создавать свои блоки, что описано тут, правда не понятно зачем этим заниматься.